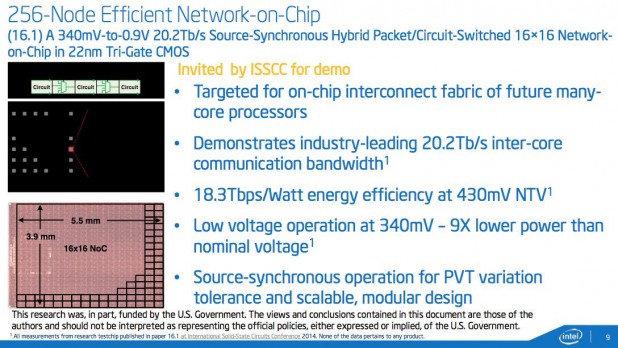

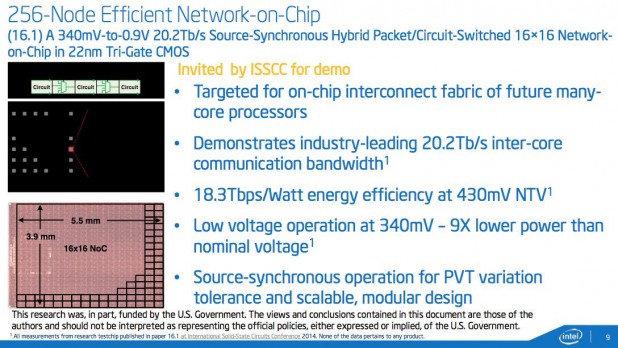

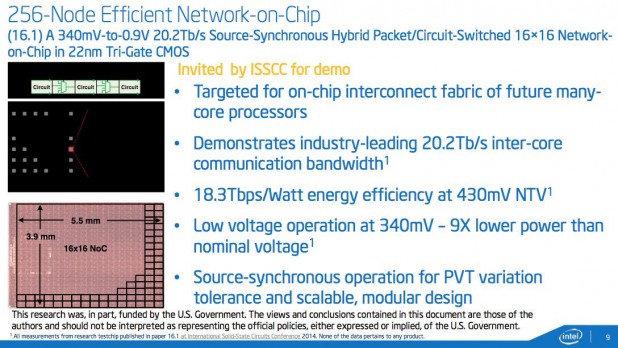

Intel combines circuit- and packet-switching to let core run at different rates.[/caption] Intel Labs is demonstrating a "network-on-a-chip" designed to make high-performance multicore processors more powerful and efficient by building a network on the chip itself that processor cores can use to communicate. Current multicore chips run all the cores at the same frequency and voltage. Ideally it would be possible to change that so the cores handling compute-heavy workloads would get more power and run faster than those dawdling along in support. Requirements of the ring buses and other inflexible mechanisms for processor cores to exchange data on-chip make that impossible, however, according to a Feb. 9 story in The Register previewing Intel's presentation at the International Solid-State Circuits Conference(ISSC) in San Francisco Feb. 9-13. Adding a global clock that would coordinate things would eat up extra space on the chip; so would circuitry to route power and data correctly, according to Vivek De, Intel Labs' Director of Circuit Technology Research, as quoted in The Register. The design Intel came up with is a mesh interconnect that uses node-to-node handshaking rather than a global clock and controls data flow with a combination of packet- and circuit-switched circuits. The result is a packet-switched micro-network on the processor that allows the cores to talk about a data transfer, then switches back to circuit-switching once the transfer starts. The demo chip contains a mesh of 256 nodes with independent voltages and clocks and aggregate throughput of 20.2 terabits/second among nodes, according to Intel's paper on the chip, which is titled: "A 340mV-to-0.9V 20.2Tb/s Source-Synchronous Hybrid Packet/Circuit-Switched 16×16 Network-on-Chip in 22nm Tri-Gate CMOS." Also at the ISSC show, Intel will demonstrate a new graphics chip built on its newest 22nm tri-gate system-on-a-chip that cuts energy use by 40 percent, with a standby mode that can cut energy use to 10 percent of current levels. The chip accomplishes that by lowering the minimum voltage level for the whole chip and boosting it selectively for small parts of the core only when extra power is needed. The chip also includes a technique called adaptive clocking that slows the clock frequency to avoid failures when the voltage level drops too low, according to Intel engineer Divya Kolar. The chip, which will be demonstrated at ISSC, could extend battery life of handheld devices and reduce the power cost of gaming by 40 percent Kolar wrote. Both chips are still research projects with no specific roadmap or schedule for inclusion in commercial products, so it may be a while before we see more than a demo. Image: Intel Corp.

Intel combines circuit- and packet-switching to let core run at different rates.[/caption] Intel Labs is demonstrating a "network-on-a-chip" designed to make high-performance multicore processors more powerful and efficient by building a network on the chip itself that processor cores can use to communicate. Current multicore chips run all the cores at the same frequency and voltage. Ideally it would be possible to change that so the cores handling compute-heavy workloads would get more power and run faster than those dawdling along in support. Requirements of the ring buses and other inflexible mechanisms for processor cores to exchange data on-chip make that impossible, however, according to a Feb. 9 story in The Register previewing Intel's presentation at the International Solid-State Circuits Conference(ISSC) in San Francisco Feb. 9-13. Adding a global clock that would coordinate things would eat up extra space on the chip; so would circuitry to route power and data correctly, according to Vivek De, Intel Labs' Director of Circuit Technology Research, as quoted in The Register. The design Intel came up with is a mesh interconnect that uses node-to-node handshaking rather than a global clock and controls data flow with a combination of packet- and circuit-switched circuits. The result is a packet-switched micro-network on the processor that allows the cores to talk about a data transfer, then switches back to circuit-switching once the transfer starts. The demo chip contains a mesh of 256 nodes with independent voltages and clocks and aggregate throughput of 20.2 terabits/second among nodes, according to Intel's paper on the chip, which is titled: "A 340mV-to-0.9V 20.2Tb/s Source-Synchronous Hybrid Packet/Circuit-Switched 16×16 Network-on-Chip in 22nm Tri-Gate CMOS." Also at the ISSC show, Intel will demonstrate a new graphics chip built on its newest 22nm tri-gate system-on-a-chip that cuts energy use by 40 percent, with a standby mode that can cut energy use to 10 percent of current levels. The chip accomplishes that by lowering the minimum voltage level for the whole chip and boosting it selectively for small parts of the core only when extra power is needed. The chip also includes a technique called adaptive clocking that slows the clock frequency to avoid failures when the voltage level drops too low, according to Intel engineer Divya Kolar. The chip, which will be demonstrated at ISSC, could extend battery life of handheld devices and reduce the power cost of gaming by 40 percent Kolar wrote. Both chips are still research projects with no specific roadmap or schedule for inclusion in commercial products, so it may be a while before we see more than a demo. Image: Intel Corp. On-Chip Network Makes Processor Run Like a Cluster

[caption id="attachment_17150" align="aligncenter" width="618"] Intel combines circuit- and packet-switching to let core run at different rates.[/caption] Intel Labs is demonstrating a "network-on-a-chip" designed to make high-performance multicore processors more powerful and efficient by building a network on the chip itself that processor cores can use to communicate. Current multicore chips run all the cores at the same frequency and voltage. Ideally it would be possible to change that so the cores handling compute-heavy workloads would get more power and run faster than those dawdling along in support. Requirements of the ring buses and other inflexible mechanisms for processor cores to exchange data on-chip make that impossible, however, according to a Feb. 9 story in The Register previewing Intel's presentation at the International Solid-State Circuits Conference(ISSC) in San Francisco Feb. 9-13. Adding a global clock that would coordinate things would eat up extra space on the chip; so would circuitry to route power and data correctly, according to Vivek De, Intel Labs' Director of Circuit Technology Research, as quoted in The Register. The design Intel came up with is a mesh interconnect that uses node-to-node handshaking rather than a global clock and controls data flow with a combination of packet- and circuit-switched circuits. The result is a packet-switched micro-network on the processor that allows the cores to talk about a data transfer, then switches back to circuit-switching once the transfer starts. The demo chip contains a mesh of 256 nodes with independent voltages and clocks and aggregate throughput of 20.2 terabits/second among nodes, according to Intel's paper on the chip, which is titled: "A 340mV-to-0.9V 20.2Tb/s Source-Synchronous Hybrid Packet/Circuit-Switched 16×16 Network-on-Chip in 22nm Tri-Gate CMOS." Also at the ISSC show, Intel will demonstrate a new graphics chip built on its newest 22nm tri-gate system-on-a-chip that cuts energy use by 40 percent, with a standby mode that can cut energy use to 10 percent of current levels. The chip accomplishes that by lowering the minimum voltage level for the whole chip and boosting it selectively for small parts of the core only when extra power is needed. The chip also includes a technique called adaptive clocking that slows the clock frequency to avoid failures when the voltage level drops too low, according to Intel engineer Divya Kolar. The chip, which will be demonstrated at ISSC, could extend battery life of handheld devices and reduce the power cost of gaming by 40 percent Kolar wrote. Both chips are still research projects with no specific roadmap or schedule for inclusion in commercial products, so it may be a while before we see more than a demo. Image: Intel Corp.

Intel combines circuit- and packet-switching to let core run at different rates.[/caption] Intel Labs is demonstrating a "network-on-a-chip" designed to make high-performance multicore processors more powerful and efficient by building a network on the chip itself that processor cores can use to communicate. Current multicore chips run all the cores at the same frequency and voltage. Ideally it would be possible to change that so the cores handling compute-heavy workloads would get more power and run faster than those dawdling along in support. Requirements of the ring buses and other inflexible mechanisms for processor cores to exchange data on-chip make that impossible, however, according to a Feb. 9 story in The Register previewing Intel's presentation at the International Solid-State Circuits Conference(ISSC) in San Francisco Feb. 9-13. Adding a global clock that would coordinate things would eat up extra space on the chip; so would circuitry to route power and data correctly, according to Vivek De, Intel Labs' Director of Circuit Technology Research, as quoted in The Register. The design Intel came up with is a mesh interconnect that uses node-to-node handshaking rather than a global clock and controls data flow with a combination of packet- and circuit-switched circuits. The result is a packet-switched micro-network on the processor that allows the cores to talk about a data transfer, then switches back to circuit-switching once the transfer starts. The demo chip contains a mesh of 256 nodes with independent voltages and clocks and aggregate throughput of 20.2 terabits/second among nodes, according to Intel's paper on the chip, which is titled: "A 340mV-to-0.9V 20.2Tb/s Source-Synchronous Hybrid Packet/Circuit-Switched 16×16 Network-on-Chip in 22nm Tri-Gate CMOS." Also at the ISSC show, Intel will demonstrate a new graphics chip built on its newest 22nm tri-gate system-on-a-chip that cuts energy use by 40 percent, with a standby mode that can cut energy use to 10 percent of current levels. The chip accomplishes that by lowering the minimum voltage level for the whole chip and boosting it selectively for small parts of the core only when extra power is needed. The chip also includes a technique called adaptive clocking that slows the clock frequency to avoid failures when the voltage level drops too low, according to Intel engineer Divya Kolar. The chip, which will be demonstrated at ISSC, could extend battery life of handheld devices and reduce the power cost of gaming by 40 percent Kolar wrote. Both chips are still research projects with no specific roadmap or schedule for inclusion in commercial products, so it may be a while before we see more than a demo. Image: Intel Corp.

Intel combines circuit- and packet-switching to let core run at different rates.[/caption] Intel Labs is demonstrating a "network-on-a-chip" designed to make high-performance multicore processors more powerful and efficient by building a network on the chip itself that processor cores can use to communicate. Current multicore chips run all the cores at the same frequency and voltage. Ideally it would be possible to change that so the cores handling compute-heavy workloads would get more power and run faster than those dawdling along in support. Requirements of the ring buses and other inflexible mechanisms for processor cores to exchange data on-chip make that impossible, however, according to a Feb. 9 story in The Register previewing Intel's presentation at the International Solid-State Circuits Conference(ISSC) in San Francisco Feb. 9-13. Adding a global clock that would coordinate things would eat up extra space on the chip; so would circuitry to route power and data correctly, according to Vivek De, Intel Labs' Director of Circuit Technology Research, as quoted in The Register. The design Intel came up with is a mesh interconnect that uses node-to-node handshaking rather than a global clock and controls data flow with a combination of packet- and circuit-switched circuits. The result is a packet-switched micro-network on the processor that allows the cores to talk about a data transfer, then switches back to circuit-switching once the transfer starts. The demo chip contains a mesh of 256 nodes with independent voltages and clocks and aggregate throughput of 20.2 terabits/second among nodes, according to Intel's paper on the chip, which is titled: "A 340mV-to-0.9V 20.2Tb/s Source-Synchronous Hybrid Packet/Circuit-Switched 16×16 Network-on-Chip in 22nm Tri-Gate CMOS." Also at the ISSC show, Intel will demonstrate a new graphics chip built on its newest 22nm tri-gate system-on-a-chip that cuts energy use by 40 percent, with a standby mode that can cut energy use to 10 percent of current levels. The chip accomplishes that by lowering the minimum voltage level for the whole chip and boosting it selectively for small parts of the core only when extra power is needed. The chip also includes a technique called adaptive clocking that slows the clock frequency to avoid failures when the voltage level drops too low, according to Intel engineer Divya Kolar. The chip, which will be demonstrated at ISSC, could extend battery life of handheld devices and reduce the power cost of gaming by 40 percent Kolar wrote. Both chips are still research projects with no specific roadmap or schedule for inclusion in commercial products, so it may be a while before we see more than a demo. Image: Intel Corp.

Intel combines circuit- and packet-switching to let core run at different rates.[/caption] Intel Labs is demonstrating a "network-on-a-chip" designed to make high-performance multicore processors more powerful and efficient by building a network on the chip itself that processor cores can use to communicate. Current multicore chips run all the cores at the same frequency and voltage. Ideally it would be possible to change that so the cores handling compute-heavy workloads would get more power and run faster than those dawdling along in support. Requirements of the ring buses and other inflexible mechanisms for processor cores to exchange data on-chip make that impossible, however, according to a Feb. 9 story in The Register previewing Intel's presentation at the International Solid-State Circuits Conference(ISSC) in San Francisco Feb. 9-13. Adding a global clock that would coordinate things would eat up extra space on the chip; so would circuitry to route power and data correctly, according to Vivek De, Intel Labs' Director of Circuit Technology Research, as quoted in The Register. The design Intel came up with is a mesh interconnect that uses node-to-node handshaking rather than a global clock and controls data flow with a combination of packet- and circuit-switched circuits. The result is a packet-switched micro-network on the processor that allows the cores to talk about a data transfer, then switches back to circuit-switching once the transfer starts. The demo chip contains a mesh of 256 nodes with independent voltages and clocks and aggregate throughput of 20.2 terabits/second among nodes, according to Intel's paper on the chip, which is titled: "A 340mV-to-0.9V 20.2Tb/s Source-Synchronous Hybrid Packet/Circuit-Switched 16×16 Network-on-Chip in 22nm Tri-Gate CMOS." Also at the ISSC show, Intel will demonstrate a new graphics chip built on its newest 22nm tri-gate system-on-a-chip that cuts energy use by 40 percent, with a standby mode that can cut energy use to 10 percent of current levels. The chip accomplishes that by lowering the minimum voltage level for the whole chip and boosting it selectively for small parts of the core only when extra power is needed. The chip also includes a technique called adaptive clocking that slows the clock frequency to avoid failures when the voltage level drops too low, according to Intel engineer Divya Kolar. The chip, which will be demonstrated at ISSC, could extend battery life of handheld devices and reduce the power cost of gaming by 40 percent Kolar wrote. Both chips are still research projects with no specific roadmap or schedule for inclusion in commercial products, so it may be a while before we see more than a demo. Image: Intel Corp.