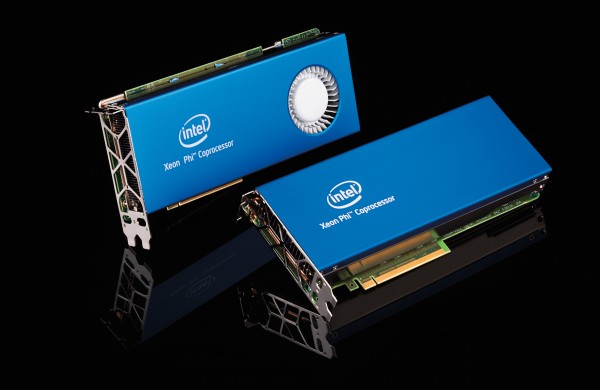

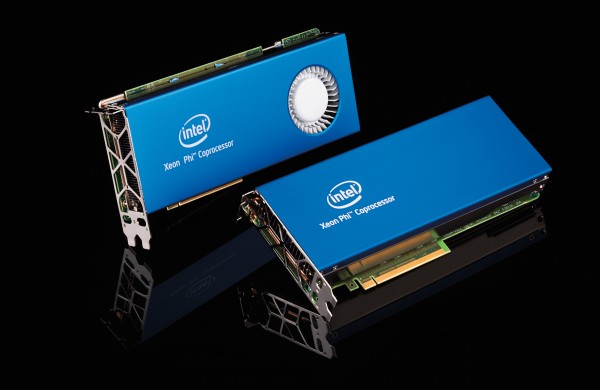

Intel’s Xeon Phi co-processor, designed to optimize computing capability in the data center, has reached its general availability milestone. Wait, you might be thinking: hasn’t Intel already announced the Xeon Phi? After all, the co-processor has appeared in supercomputers, including the TACC Stampede, and Intel hasn’t exactly made a secret of its “many core” architecture, which dates back several years. The Xeon Phi was originally code-named “Knights Ferry.” That’s true, but Intel has now released the coprocessors for general availability. They come in two flavors: the Xeon Phi 3100 and the Xeon Phi 5100P. The Xeon Phi 3100 will produce more than a teraflop of performance, with 240 GB/s bandwidth and support for up to 6 GB of memory, operating within a 300-watt thermal band. The 5110P, on the other hand, is passively cooled, and runs within a 225-watt TDP band. Performance is on the order of 1.011 teraflops, supporting 320 GB/s memory bandwidth and up to 8 GB of GDDR-5 memory. Intel didn’t release the specifications of the Xeon Phi 3100, but said that the 5110P would include 60 cores running at 1.053 GHz, with a total of 240 threads. Both use Intel’s 22-nm process technology. (The versions of the Xeon Phi used by supercomputers like the Stampede were customized chips, which include the Intel Xeon Phi coprocessor SE10X and Intel Xeon Phi coprocessor SE10P. These offer 1073 GFLOPS, double-precision performance at 300 watts, Intel said, and are otherwise similar to Intel Xeon Phi 5110P coprocessor.) The new Xeon Phis are designed to be paired with the Xeon E5-2600/4600, processor families that Intel correctly noted make up many of the processor architectures used by the recent TOP500 list of the world’s fastest supercomputers. Xeon Phi co-processors are also used within the “Beacon” supercomputer, rated among the most power-efficient at 157.5 TFLOPS (Rpeak) at 45.11 kW. “Intel Xeon Phi coprocessor represents an achievement in Intel innovation that will help propel us to new heights in research and discovery, and reaffirms our commitment to Exascale-level computing,” said Diane Bryant, vice president and general manager of the Datacenter and Connected Systems Group. “The combination of the Intel Xeon processor family and the Intel Xeon Phi coprocessor will change the scope and scale of what highly parallel applications can accomplish, by delivering unprecedented performance, efficiency and programmability. With this technology as a new foundation for HPC, solving real-world challenges from accurately predicting weather patterns 21 days in advance, to developing new cures for diseases will become increasingly possible.” Intel’s Xeon Phi dates way back to 2008, when the company first disclosed, via a SIGGRAPH research paper, that it intended to bring to market a “many core” graphics chip, separate from the integrated graphics cores that now form the foundation of many notebook PCs. But the “Larrabee” chip was canned in Dec. 2009, and the underlying MIC architecture re-purposed for what became Knights Ferry and later Knights Bridge. Intel positioned the chips as ideal for HPC and other applications that require large amounts of repetitive-yet-efficient number crunching. Mozilla chief technical officer Brendan Eich, for example, has demonstrated “River Trail,” a 3D n-body simulation that can harness the Xeon Phi architecture to dramatically improve performance. Intel has also brought executives from CERN and its Large Hadron Collider onstage to talk about how Intel’s chip, using the Knights Ferry development platform, has smoothed the processing of terabytes of data. The Intel Xeon Phi coprocessor 5110P is shipping today with general availability on Jan. 28, and recommended customer price of $2,649. The Intel Xeon Phi coprocessor 3100 product family will be available during the first half of 2013 with a recommended customer price below $2,000. Image: Intel

Intel’s Xeon Phi co-processor, designed to optimize computing capability in the data center, has reached its general availability milestone. Wait, you might be thinking: hasn’t Intel already announced the Xeon Phi? After all, the co-processor has appeared in supercomputers, including the TACC Stampede, and Intel hasn’t exactly made a secret of its “many core” architecture, which dates back several years. The Xeon Phi was originally code-named “Knights Ferry.” That’s true, but Intel has now released the coprocessors for general availability. They come in two flavors: the Xeon Phi 3100 and the Xeon Phi 5100P. The Xeon Phi 3100 will produce more than a teraflop of performance, with 240 GB/s bandwidth and support for up to 6 GB of memory, operating within a 300-watt thermal band. The 5110P, on the other hand, is passively cooled, and runs within a 225-watt TDP band. Performance is on the order of 1.011 teraflops, supporting 320 GB/s memory bandwidth and up to 8 GB of GDDR-5 memory. Intel didn’t release the specifications of the Xeon Phi 3100, but said that the 5110P would include 60 cores running at 1.053 GHz, with a total of 240 threads. Both use Intel’s 22-nm process technology. (The versions of the Xeon Phi used by supercomputers like the Stampede were customized chips, which include the Intel Xeon Phi coprocessor SE10X and Intel Xeon Phi coprocessor SE10P. These offer 1073 GFLOPS, double-precision performance at 300 watts, Intel said, and are otherwise similar to Intel Xeon Phi 5110P coprocessor.) The new Xeon Phis are designed to be paired with the Xeon E5-2600/4600, processor families that Intel correctly noted make up many of the processor architectures used by the recent TOP500 list of the world’s fastest supercomputers. Xeon Phi co-processors are also used within the “Beacon” supercomputer, rated among the most power-efficient at 157.5 TFLOPS (Rpeak) at 45.11 kW. “Intel Xeon Phi coprocessor represents an achievement in Intel innovation that will help propel us to new heights in research and discovery, and reaffirms our commitment to Exascale-level computing,” said Diane Bryant, vice president and general manager of the Datacenter and Connected Systems Group. “The combination of the Intel Xeon processor family and the Intel Xeon Phi coprocessor will change the scope and scale of what highly parallel applications can accomplish, by delivering unprecedented performance, efficiency and programmability. With this technology as a new foundation for HPC, solving real-world challenges from accurately predicting weather patterns 21 days in advance, to developing new cures for diseases will become increasingly possible.” Intel’s Xeon Phi dates way back to 2008, when the company first disclosed, via a SIGGRAPH research paper, that it intended to bring to market a “many core” graphics chip, separate from the integrated graphics cores that now form the foundation of many notebook PCs. But the “Larrabee” chip was canned in Dec. 2009, and the underlying MIC architecture re-purposed for what became Knights Ferry and later Knights Bridge. Intel positioned the chips as ideal for HPC and other applications that require large amounts of repetitive-yet-efficient number crunching. Mozilla chief technical officer Brendan Eich, for example, has demonstrated “River Trail,” a 3D n-body simulation that can harness the Xeon Phi architecture to dramatically improve performance. Intel has also brought executives from CERN and its Large Hadron Collider onstage to talk about how Intel’s chip, using the Knights Ferry development platform, has smoothed the processing of terabytes of data. The Intel Xeon Phi coprocessor 5110P is shipping today with general availability on Jan. 28, and recommended customer price of $2,649. The Intel Xeon Phi coprocessor 3100 product family will be available during the first half of 2013 with a recommended customer price below $2,000. Image: Intel Intel Formally Launches Xeon Phi Coprocessors

Intel’s Xeon Phi co-processor, designed to optimize computing capability in the data center, has reached its general availability milestone. Wait, you might be thinking: hasn’t Intel already announced the Xeon Phi? After all, the co-processor has appeared in supercomputers, including the TACC Stampede, and Intel hasn’t exactly made a secret of its “many core” architecture, which dates back several years. The Xeon Phi was originally code-named “Knights Ferry.” That’s true, but Intel has now released the coprocessors for general availability. They come in two flavors: the Xeon Phi 3100 and the Xeon Phi 5100P. The Xeon Phi 3100 will produce more than a teraflop of performance, with 240 GB/s bandwidth and support for up to 6 GB of memory, operating within a 300-watt thermal band. The 5110P, on the other hand, is passively cooled, and runs within a 225-watt TDP band. Performance is on the order of 1.011 teraflops, supporting 320 GB/s memory bandwidth and up to 8 GB of GDDR-5 memory. Intel didn’t release the specifications of the Xeon Phi 3100, but said that the 5110P would include 60 cores running at 1.053 GHz, with a total of 240 threads. Both use Intel’s 22-nm process technology. (The versions of the Xeon Phi used by supercomputers like the Stampede were customized chips, which include the Intel Xeon Phi coprocessor SE10X and Intel Xeon Phi coprocessor SE10P. These offer 1073 GFLOPS, double-precision performance at 300 watts, Intel said, and are otherwise similar to Intel Xeon Phi 5110P coprocessor.) The new Xeon Phis are designed to be paired with the Xeon E5-2600/4600, processor families that Intel correctly noted make up many of the processor architectures used by the recent TOP500 list of the world’s fastest supercomputers. Xeon Phi co-processors are also used within the “Beacon” supercomputer, rated among the most power-efficient at 157.5 TFLOPS (Rpeak) at 45.11 kW. “Intel Xeon Phi coprocessor represents an achievement in Intel innovation that will help propel us to new heights in research and discovery, and reaffirms our commitment to Exascale-level computing,” said Diane Bryant, vice president and general manager of the Datacenter and Connected Systems Group. “The combination of the Intel Xeon processor family and the Intel Xeon Phi coprocessor will change the scope and scale of what highly parallel applications can accomplish, by delivering unprecedented performance, efficiency and programmability. With this technology as a new foundation for HPC, solving real-world challenges from accurately predicting weather patterns 21 days in advance, to developing new cures for diseases will become increasingly possible.” Intel’s Xeon Phi dates way back to 2008, when the company first disclosed, via a SIGGRAPH research paper, that it intended to bring to market a “many core” graphics chip, separate from the integrated graphics cores that now form the foundation of many notebook PCs. But the “Larrabee” chip was canned in Dec. 2009, and the underlying MIC architecture re-purposed for what became Knights Ferry and later Knights Bridge. Intel positioned the chips as ideal for HPC and other applications that require large amounts of repetitive-yet-efficient number crunching. Mozilla chief technical officer Brendan Eich, for example, has demonstrated “River Trail,” a 3D n-body simulation that can harness the Xeon Phi architecture to dramatically improve performance. Intel has also brought executives from CERN and its Large Hadron Collider onstage to talk about how Intel’s chip, using the Knights Ferry development platform, has smoothed the processing of terabytes of data. The Intel Xeon Phi coprocessor 5110P is shipping today with general availability on Jan. 28, and recommended customer price of $2,649. The Intel Xeon Phi coprocessor 3100 product family will be available during the first half of 2013 with a recommended customer price below $2,000. Image: Intel

Intel’s Xeon Phi co-processor, designed to optimize computing capability in the data center, has reached its general availability milestone. Wait, you might be thinking: hasn’t Intel already announced the Xeon Phi? After all, the co-processor has appeared in supercomputers, including the TACC Stampede, and Intel hasn’t exactly made a secret of its “many core” architecture, which dates back several years. The Xeon Phi was originally code-named “Knights Ferry.” That’s true, but Intel has now released the coprocessors for general availability. They come in two flavors: the Xeon Phi 3100 and the Xeon Phi 5100P. The Xeon Phi 3100 will produce more than a teraflop of performance, with 240 GB/s bandwidth and support for up to 6 GB of memory, operating within a 300-watt thermal band. The 5110P, on the other hand, is passively cooled, and runs within a 225-watt TDP band. Performance is on the order of 1.011 teraflops, supporting 320 GB/s memory bandwidth and up to 8 GB of GDDR-5 memory. Intel didn’t release the specifications of the Xeon Phi 3100, but said that the 5110P would include 60 cores running at 1.053 GHz, with a total of 240 threads. Both use Intel’s 22-nm process technology. (The versions of the Xeon Phi used by supercomputers like the Stampede were customized chips, which include the Intel Xeon Phi coprocessor SE10X and Intel Xeon Phi coprocessor SE10P. These offer 1073 GFLOPS, double-precision performance at 300 watts, Intel said, and are otherwise similar to Intel Xeon Phi 5110P coprocessor.) The new Xeon Phis are designed to be paired with the Xeon E5-2600/4600, processor families that Intel correctly noted make up many of the processor architectures used by the recent TOP500 list of the world’s fastest supercomputers. Xeon Phi co-processors are also used within the “Beacon” supercomputer, rated among the most power-efficient at 157.5 TFLOPS (Rpeak) at 45.11 kW. “Intel Xeon Phi coprocessor represents an achievement in Intel innovation that will help propel us to new heights in research and discovery, and reaffirms our commitment to Exascale-level computing,” said Diane Bryant, vice president and general manager of the Datacenter and Connected Systems Group. “The combination of the Intel Xeon processor family and the Intel Xeon Phi coprocessor will change the scope and scale of what highly parallel applications can accomplish, by delivering unprecedented performance, efficiency and programmability. With this technology as a new foundation for HPC, solving real-world challenges from accurately predicting weather patterns 21 days in advance, to developing new cures for diseases will become increasingly possible.” Intel’s Xeon Phi dates way back to 2008, when the company first disclosed, via a SIGGRAPH research paper, that it intended to bring to market a “many core” graphics chip, separate from the integrated graphics cores that now form the foundation of many notebook PCs. But the “Larrabee” chip was canned in Dec. 2009, and the underlying MIC architecture re-purposed for what became Knights Ferry and later Knights Bridge. Intel positioned the chips as ideal for HPC and other applications that require large amounts of repetitive-yet-efficient number crunching. Mozilla chief technical officer Brendan Eich, for example, has demonstrated “River Trail,” a 3D n-body simulation that can harness the Xeon Phi architecture to dramatically improve performance. Intel has also brought executives from CERN and its Large Hadron Collider onstage to talk about how Intel’s chip, using the Knights Ferry development platform, has smoothed the processing of terabytes of data. The Intel Xeon Phi coprocessor 5110P is shipping today with general availability on Jan. 28, and recommended customer price of $2,649. The Intel Xeon Phi coprocessor 3100 product family will be available during the first half of 2013 with a recommended customer price below $2,000. Image: Intel